大家好,小裕来为大家解答以上问题。加法器的基本原理,加法器的设计原理这个很多人还不清楚,现在一起跟着小编来瞧瞧吧!

1、 加法器是数字系统中的基本逻辑器件,减法器和硬件乘法器都可以由加法器组成。

2、 因此,它常常是数字信号处理系统中的限速元件。

3、 通过精心优化加法器,可以得到速度快、面积小的电路,同时大大提高数字系统的整体性能。

4、 加法器设计概述目前多位加法器主要有两种,串行进位和并行进位。

5、 并行进位加法器具有进位生成逻辑,运算速度快。

6、 串行进位加法器是由所有加法器级联而成的多位加法器。

7、 并行进位加法器通常比串行级联加法器占用更多的资源。

8、 随着位数的增加,相同位数的并行加法器和串行加法器之间的差距越来越大。

9、 因此,在工程实践中,加法器的选择往往需要在速度和容量之间进行折衷,从而找到合适的应用方案。

10、 并行加法器是并行的,但各级全加器还是级联的。这是因为FPGA采用查找表的原理实现加法功能,所以不需要优化内部CMOS进位链的结构就可以直接实现并行加法功能。

关于加法器的基本原理,加法器的设计原理的介绍到此结束,希望对大家有所帮助。

智能推荐

-

山姆泡面桶炒至500元仍遭疯抢 因设计新颖迅速风靡2023-09-10 音频解说山姆泡面桶炒至5元仍遭疯抢因设计新颖迅速风靡今天的关注度非常高,直接上了热搜榜,那么具体的是什么情况呢,大家可以一起来看看具体都是怎么回事吧

-

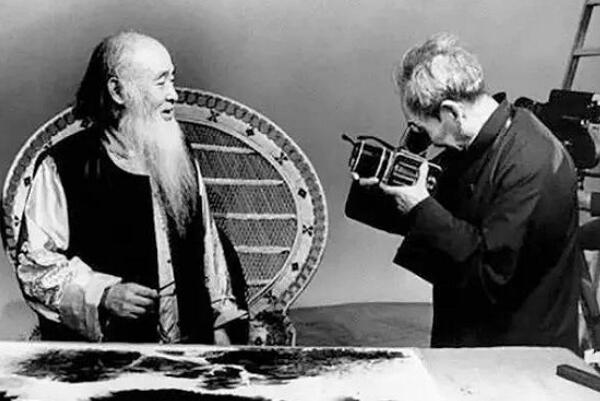

[中国十大著名摄影师,肖全上榜,第一将中国绘画原理应用到摄影上]2023-08-29 导语:影相师是使用照相机、感光片、光源和外型技术在室内外拍摄图象新闻的职员,在手机影相还未普通前,找影相师拍照就成为主流,而今虽有多量影相爱好者可和专业影相师比拟

-

包装与设计杂志期刊信息(包装设计论文参考文献最新)2023-08-07 包装与设计杂志简介本站紧要处置期刊订阅及增值电信生意中的新闻服务生意(互联网新闻服务),并非包装与设计杂志官方网站

-

艺术设计研究杂志艺术国家级期刊投稿(艺术设计类期刊)2023-08-24 艺术设计研究杂志社简介艺术设计研究(季刊)创刊于1992年,由北京服装学院主理。是国内艺术设计规模的要紧学术期刊,严重登载艺术学规模最新的讲授和科研成果,推出国内

-

宜家app如何自己设计衣柜 宜家家居app添加设计方案教程2023-09-09 开启IKEA宜家家居,选择个人核心的【我的设计方案】。在开启的页面中,选择【设计新方案】。在开启的页面中,选择【添加】

-

浮选机的基本作用(浮选机工作原理)2023-08-07 大家好,小讯来为大家解答以上的问题。浮选机的基本作用,浮选机工作原理这个很多人还不知道,现在让我们一起来看看吧

-

霍金辐射有什么用(霍金辐射的原理是什么)2023-08-29 大家好,小裕来为大家解答以上问题。霍金辐射有什么用,霍金辐射的原理是什么这个很多人还不清楚,现在一起跟着小编来瞧瞧吧

-

看着不错,实际却非常“脏”的10个家居设计!2023-08-24 看着不错,实际却非常“脏”的10个家居设计!,瓷砖,地毯,窗帘,哑光,绒布,家居设计

-

为了不被冲烂,我们决定设计一套完美的游戏评分方案2023-08-06 为了不被冲烂,我们决定设计一套完美的游戏评分方案,游戏,最终幻想,黑暗之魂,电子游戏

-

小熊字体设计(小熊字体)2023-07-29 大家好,小讯来为大家解答以上的问题。小熊字体设计,小熊字体这个很多人还不知道,现在让我们一起来看看吧

-

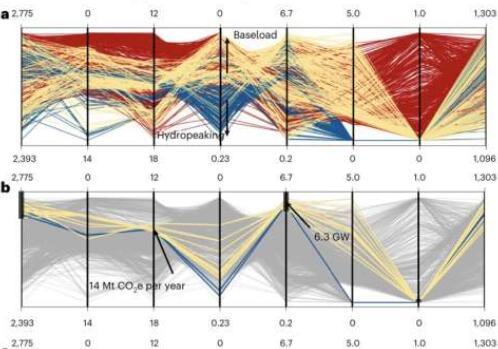

低排放能源系统在没有智能设计的情况下可能会产生水冲突2023-08-08 今天发表在《自然可持续发展》杂志上的一项新研究发现,除非采用智能设计,否则使用水电大坝产生低排放能源可能会给食品生产等其他经济部门带来问题

-

下雪天撒盐的原理(下雪天)2023-08-08 大家好,小讯来为大家解答以上的问题。下雪天撒盐的原理,下雪天这个很多人还不知道,现在让我们一起来看看吧